Gen-3 Experimental Full-Duplex Radio

As part of our continued experimentation into wideband full-duplex (FD) wireless, we are developing a FD radio system using a novel FIR canceller with variable weights and delays. A self-interference (SI) canceller was implemented on an integrated circuit (IC) which provides cancellation in both the radio frequency (RF) and analog baseband (BB) domains [3,4].

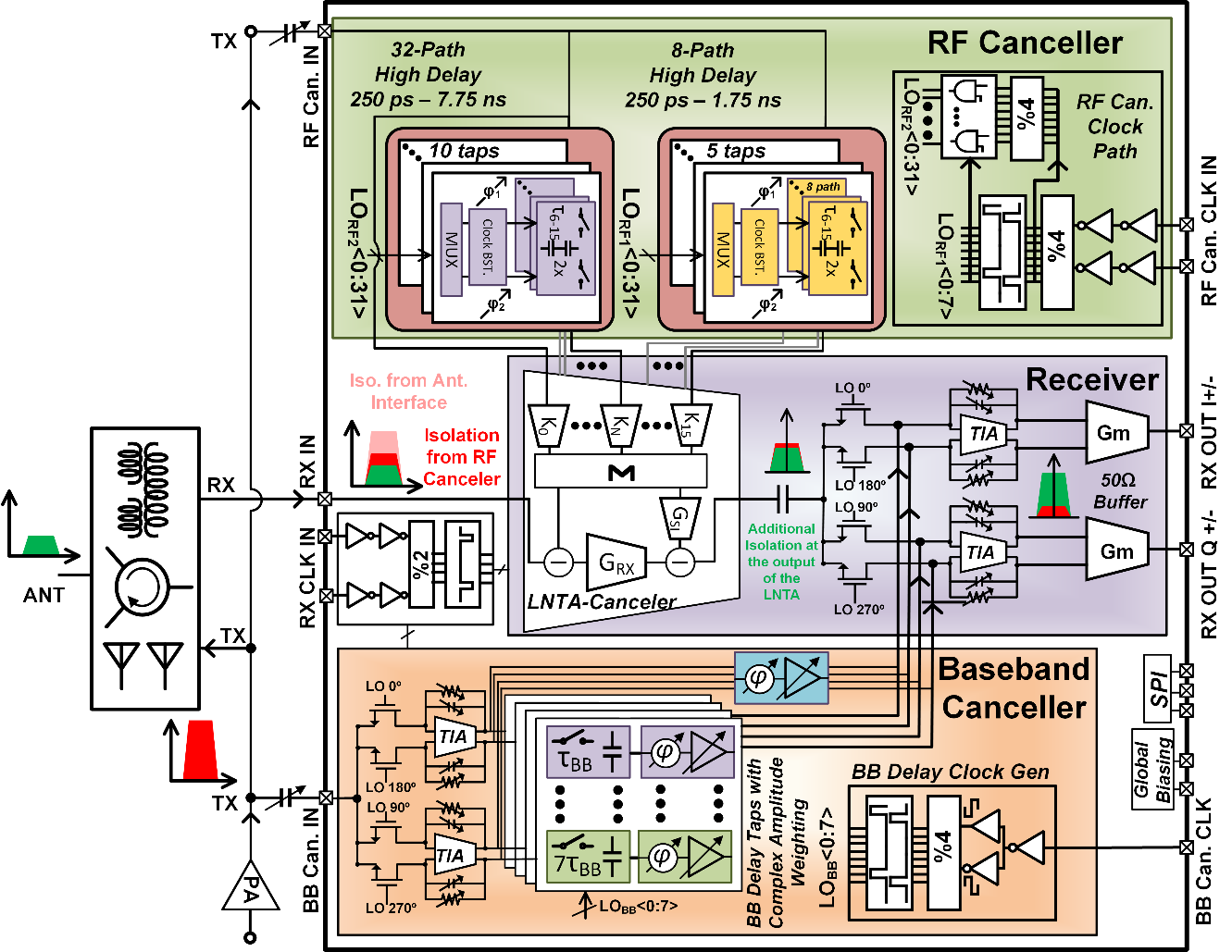

The IC uses switched-capacitor-based time-interleaved circuits to achieve large reconfigurable delays with low loss and compact form factor. As shown in the figure below, the IC leverages a 16-tap RF canceler operating across DC to 1GHz with delays ranging from 0.25ps to 8ns and a complex-weighted 8-tap BB canceler with delays ranging from 10ns to 85ns in order to achieve tunable, wideband SI suppression across 200MHz to 1GHz.

To maximize SIC, the canceller IC must be configured with the optimal tap settings (gains and delays for both the RF and BB filters. However, there are three main challenges with selecting the optimal configuration:

- The large number (> 1019) of possible parameter choices across the 16 RF and 8 BB taps;

- The non-ideal response of the hardware implementation that may deviate from the analytical model;

- The quantization of gain and delay choices.

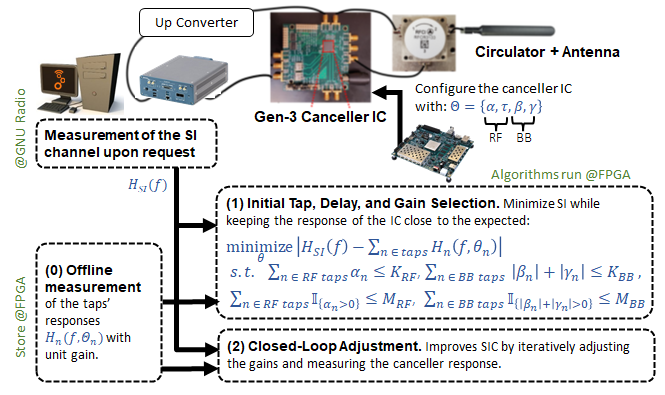

To this end, we have been developing the following full-duplex system architecture and canceller configuration algorithm, as shown in the figure below. A preliminary version of this system was demonstrated in [2], and will be demonstrated in [1] at SIGCOMM 2023.

The Gen-3 Full-Duplex Radio consists of the following primary components:

- An National Instruments (NI)/Ettus Research Universal Software Radio Peripheral (USRP) 2974 software-defined radio (SDR) [link], which periodically transmits OFDM packets using variable bandwidth (10 MHz, 20 MHz, 50 MHz, and 100 MHz);

- The Gen-3 canceller IC, which performs RF and BB cancellation based on its programmed configuration;

- A Host PC operating GNU Radio 3.8 and UHD 4.2, which computes the self-interference channel and acts as a controller for the FPGA;

- A Zynq UltraScale+ MPSoC ZCU104 Evaluation Kit [link], which runs both the canceller initialization algorithm and the closed-loop adjustment aiming to compute the canceller configuration that maximizes SIC;

- A circulator-based antenna interface, which provides initial SI isolation.

References

-

Alon S. Levin, Igor Kadota, Sasank Garikapati, Bo Zhang, Aditya Jolly, Manav Kohli, Mingoo Seok, Harish Krishnaswamy, Gil Zussman, "Demo: Experimentation with Wideband Real-Time Adaptive Full-Duplex Radios," ACM SIGCOMM'23, New York, NY, Sept. 2023. [Accepted for publication]

-

Igor Kadota*, Alon S. Levin*, Bo Zhang*, Sasank Garikapati, Aditya Jolly, Manav Kohli, Tingjun Chen, Mingoo Seok, Harish Krishnaswamy, and Gil Zussman, "Adaptive Configuration of a Variable-Gain, Variable-Delay Self-Interference Canceller for a Full-Duplex System," DARPA MTO WARP End of Phase Review, Fort Worth, TX, Jun. 2022. (* indicate equal contributions)

-

Aravind Nagulu, Sasank Garikapati, Igor Kadota, Mostafa Essawy, Tingjun Chen, Arun Natarajan, Gil Zussman and Harish Krishnaswamy, “A Full-Duplex Wireless Node With CMOS Circulator and a Full-Duplex Receiver With Switched-Capacitor Delay Based Cancelers,” Demo in Proc. IEEE ISSCC'21, Feb. 2021. [video]

-

Aravind Nagulu, Sasank Garikapati, Igor Kadota, Mostafa Essawy, Tingjun Chen, Arun Natarajan, Gil Zussman, and Harish Krishnaswamy, “Full-duplex receiver with wideband multi-domain FIR cancellation based on stacked-capacitor, N-path switched-capacitor delay lines achieving >+54dB SIC Across 80MHz BW and >+15dBm TX power handling,” in Proc. IEEE ISSCC’21, Feb. 2021. [download]